|

|

Tiến sỹ Bhavya Daya, khoa Kỹ thuật điện và Khoa học máy tính của MIT cho biết thiết kết chip mới giảm thiểu số lượng các chu kỳ cần thiết để thực hiện tác vụ bằng cách cho phép truyền dữ liệu giữa các nhân (core) và bộ nhớ đệm (cache) chặt chẽ hơn.

Ông cũng tiết lộ thêm với các bộ định tuyến mini, các nhà nghiên cứu tại MIT đã phát minh ra cách mới để định tuyến lại các gói dữ liệu và mở rộng băng thông trong chip đa nhân ngày nay.

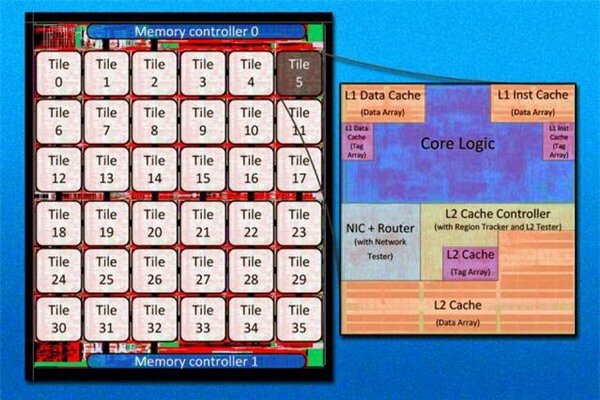

Hầu hết các bộ xử lý 4 hay 8 nhân ngày nay đều được ứng dụng kiến trúc bus gồm một đường dẫn chính kết nối các nhân với nhau để truyền dữ liệu. Hạn chế của kiến trúc này ở chỗ nếu 2 nhân làm việc cùng nhau thì những nhân còn lại sẽ mất thời gian chờ đợi. Như vậy, việc tích hợp thêm nhiều nhân xử lý chỉ làm vấn đề thêm phần phức tạp. May mắn là các nhà nghiên cứu tại MIT đã có cách giải quyết vấn đề qua việc giới thiệu bộ xử lý 36 nhân của họ.

Chip 36 nhân thế hệ mới hoạt động bằng cách sử dụng một hệ thống mạng tên gọi “network-on-a-chip” giúp việc truyền dữ liệu giữa các nhân được hiệu quả hơn thiết kế bus đặc trưng của bộ xử lý hiện tại.

Trong thiết kế “network-on-a-chip”, các nhân xử lý được sắp xếp theo dạng lát gạch và có khả năng kết nối trực tiếp với các nhân cận kề. Điều này cũng đồng nghĩa với dữ liệu có thể di chuyển theo những tuyến khác nhau để tránh nghẽn mạch tại những nhân đang xử lý tác vụ nào đó. Điều này giúp hiệu năng tổng thể của bộ xử lý cải thiện đáng kể.

|

|

Nhóm nghiên cứu cũng phát triển một mạng lưới khác tên gọi “Shadow network” trên chip 36 nhân này, cho phép các nhân chia sẻ lẫn nhau gói dữ liệu liên quan đến tác vụ đang xử lý. Tương tự cách mà các bộ xử lý đa nhân kiến trúc bus hiện nay vẫn thực hiện. Nói một cách ngắn gọn, “Shadow network” giúp đảm bảo băng thông và dữ liệu được truyền đi một cách có trật tự hơn.

Theo Bhavya Daya, hiệu suất của chip 36 nhân áp dụng thiết kế “Shadow network” được cải thiện đến 24,1% so với các chip đa nhân thông thường. Chip 36 nhân này cũng được thiết kế trên quy trình 45nm với các nhân xử lý do Freescale Semiconductor, công ty chuyên sản xuất các phần cứng nhúng cung cấp.

MIT hiện đang tiếp tục tìm kiếm cách thức tái cấu trúc bộ nhớ và băng thông nhằm cải thiện hiệu suất bộ xử lý tốt hơn. Năm ngoái, MIT đã nghiên cứu phát triển bộ xử lý có đến 110 nhân, chia sẻ bộ nhớ trực tiếp giữa các nhân mà không cần đến cache. MIT dự kiến sẽ tinh chỉnh một phiên bản hệ điều hành Linux để chạy chip 36 nhân này nhằm theo dõi những ứng dụng hoạt động thực sự như thế nào trên kiến trúc mới.